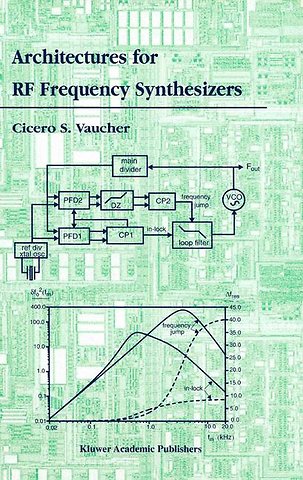

Architectures for RF Frequency Synthesizers

Samenvatting

This text describes a conceptual framework for analyzing the performance of PLL frequency synthesizers, and presents optimization procedures for the different performance aspects. It contains basic information and in-depth knowledge, widely illustrated with practical design examples used in industrial products.

Specificaties

Inhoudsopgave

1. Introduction.

2. Tuning System Specifications.

3. Single-Loop Architectures.

4. Wide-Band Architectures.

5. Adaptive PLL Architecture.

6. Programmable Dividers.

7. Conclusions.

A. PLL Stability Limits Due to the Discrete-Time PFD/CP Operation.

B. Clock-Conversion PLLs for Optical Transmitters.

About the Author. Index.