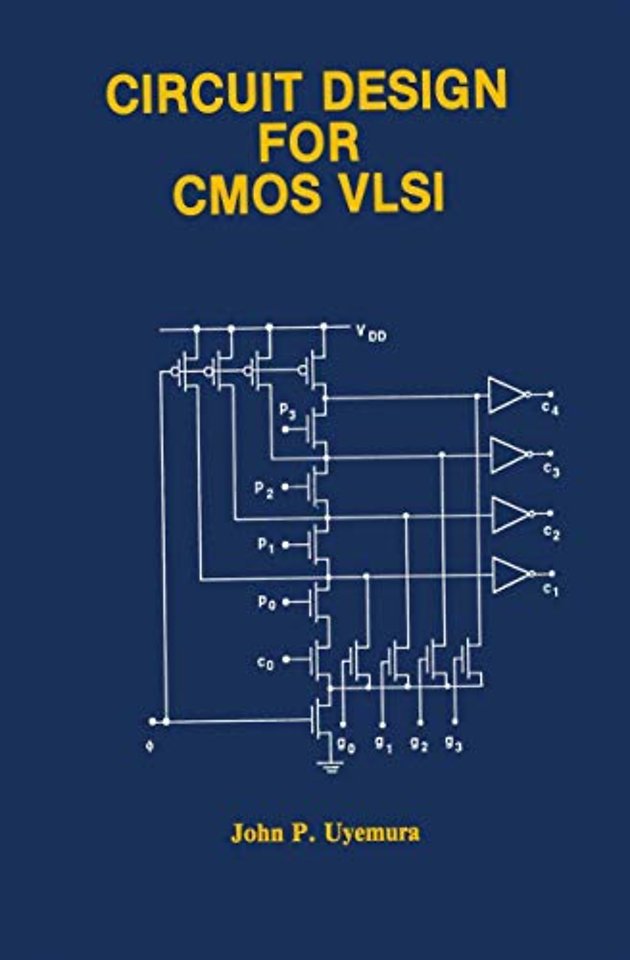

Circuit Design for CMOS VLSI

Samenvatting

During the last decade, CMOS has become increasingly attractive as a basic integrated circuit technology due to its low power (at moderate frequencies), good scalability, and rail-to-rail operation. There are now a variety of CMOS circuit styles, some based on static complementary con ductance properties, but others borrowing from earlier NMOS techniques and the advantages of using clocking disciplines for precharge-evaluate se quencing. In this comprehensive book, the reader is led systematically through the entire range of CMOS circuit design. Starting with the in dividual MOSFET, basic circuit building blocks are described, leading to a broad view of both combinatorial and sequential circuits. Once these circuits are considered in the light of CMOS process technologies, impor tant topics in circuit performance are considered, including characteristics of interconnect, gate delay, device sizing, and I/O buffering. Basic circuits are then composed to form macro elements such as multipliers, where the reader acquires a unified view of architectural performance through par allelism, and circuit performance through careful attention to circuit-level and layout design optimization. Topics in analog circuit design reflect the growing tendency for both analog and digital circuit forms to be combined on the same chip, and a careful treatment of BiCMOS forms introduces the reader to the combination of both FET and bipolar technologies on the same chip to provide improved performance.